一、印制電路板的規劃對單片機體系能否抗攪擾非常重要。要本著盡量控制噪聲源,盡量減小噪聲的傳播與耦合,盡量減小吸收這三大原則規劃印制電路板和布線。

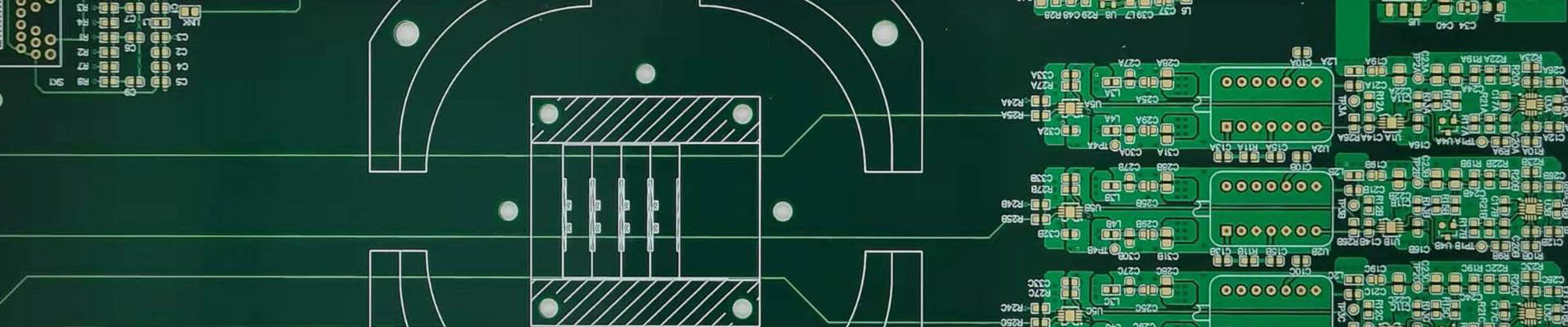

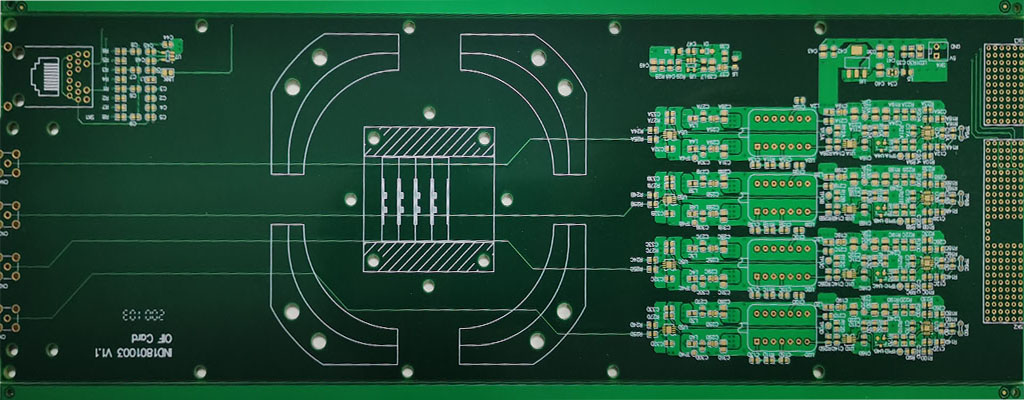

1、印制電路板要合理分區,單片機體系一般可分為三區,即模仿電路區(怕攪擾),數字電路區(抗攪擾,又發生攪擾),功率驅動區(攪擾源)。

2、印制板單點接地原則送電。三個區域的電源線,地線由該點分三路引出,噪聲元件與非噪聲元件要離得遠一些。

3、時鐘震蕩電路,特別高速邏輯電路部分用地線圈起來,讓周文電場趨近于零。

4、I/O驅動器材,功率放大器材盡量接近印制板的邊,接近引出接插件。

5、能用滿意體系最低要求頻率的時鐘,時鐘發生器要盡量接近用到該時鐘的器材。

6、石英晶體振蕩器外殼要接地,時鐘線要盡量短,且不要引得到處都是。

7、運用45度的折線布線,不要運用90度折線,以減小音頻信號的發射。

8、單面板,雙面板,電源線,地線要盡量粗,信號線的過孔要盡量少。

9、四層板比雙面板噪聲低20dB,6層板比4層板噪聲低10dB.經濟條件允許時盡量用多層板。

10、要害的線盡量短并且要粗,并在兩邊加上保護地,將靈敏信號和噪聲場帶信號通過一條扁帶電纜引出的話,要用地線--信號--地線方式引出。

11、石英振蕩器下面不要形成環路,如不可避免,環路應盡量小。

12、時鐘線垂直于I/O線比平行于I/O線攪擾小,時鐘線要遠離I/O線。

13、對A/D類器材。數字部分可繞一下也不要交叉,噪聲靈敏線不要與高速線、大電流平行。

14、單片機及其他IC電路,如有多個電源、地端的話,每端都要加一個去耦電容。

15、每個IC要有一個去偶電容,要選擇信號好的獨石電容作去耦電容。去耦電容焊在印制電路板上時,引腳要盡量短。

16、從高噪聲區的信號要加濾波,繼電器線圈處要加放電二極管。能夠用一個電陰的方法來軟化IO線的跳變沿或提供必定的阻尼。

17、用長容量的鉭電容或聚脂電容而不必電解電容作電路充電的儲能電容。因為電解電容散布電感較大,對高頻無效,運用電解電容時要與高特效好的去耦電容成對運用。

18、需求時,電源線、地線上可加用銅線繞制鐵氧體而成的高頻扼流器材阻斷高頻噪聲的傳導。

19、弱信號引出線,高頻,大功率引出電纜要加屏蔽,引出線與地線要絞起來。

20、印制板過大或信號線頻率過高,使得線上的延遲時間大于或等于信號上升時間時,該線要按傳輸線處理,要加終端匹配電阻。

21、盡量不要運用IC插座,把IC直接焊在印制板上,IC座有較大的散布電容。

二、去耦電容

每個IC的電源,地之間應配一個去耦電容,它能夠濾掉來自電源的高頻噪聲。作為儲能元件,它吸收或提供IC內部三極管導通,截止引起的電流改變,然后降低體系噪聲。要選高頻特效好的獨石電容或瓷片電容的纏繞式結構,其散布電感較大,對濾除高頻信號幾乎不起作用,作用時要與去耦電容成對運用。鉭電容則比電解電容作用更好。

三、抑制高頻電感

用粗漆包線穿入軸向有幾個孔的鐵氧體芯,就構成了高頻扼制器材。將其竄入電源線或地線中可阻撓高頻信號從電源/地線引進。這種元件特別適合用于隔開一塊印制電路板上的模仿電路區、數字電路區,以及大功率驅動的供電。應該注意的是它必須放在該區儲能電容與電源之間,而不能放在儲能電容與用電器之間。

四、低噪聲系列單片機

傳統的IC規劃中,在電源、地的引出上一般將其安排在對稱的兩邊,如左下角是地,右下角是電源,這使得電源噪聲穿過整個硅片。改善的技能將電源、地安排在兩個相鄰的引腳上,這樣一方面降低了穿過整個硅的流,一方面使外部去耦電容在PCB規劃上更簡單安排,以降低體系噪聲。另一在IC規劃上降噪聲的比如是驅動電路的規劃。一些單片機提供若干個大電流的輸出引腳,從記事毫安到數百毫安。這些大功率的驅動電路集成到單片機內部無疑增加了噪聲源。而跳變沿的軟化技能可消除這方面的影響。方法是將一個大功率管做成若干個小管子的并聯,再為每個管子輸出端串不同等效阻值電阻,以降低噪聲源。